USE DISCOUNT CODEEXPERT30TO SAVE $30 USD

matching via impedance with the PCB track

gyuunyuu1989 , 04-15-2023, 08:32 PM

Lets assume that we have a 50ohm characteristic impedance PCB track to carry high speed signal. Now, we need to use a via. The issue with via is that by default it does not have a reference plane and its size will be different from the PCB track which means an impedance discontinuity. How do designers keep this impedance discontinuity to a minimum? Is it better to avoid vias altogether?

Paul van Avesaath , 04-18-2023, 07:53 AM

you need to add GND via's next to your via transistion, also you need to calculate the copper cutout around the via's to make them a s trnasparent as posisble. (use the saturn PCB toolkit) keep spacing of the gnd via as close as possible and you should always keep them at the same distance fo your trace. a minimum of 2 is usfficient more is better but equally spaced around yout via

as example

as example

robertferanec , 04-18-2023, 08:41 AM

Unless you go above 5GHz, you don't really need to think much about via "impedance" (but you may need to add the stitching VIAs as @Paul van Avesaath mentioned ). I made some videos on via topics which can help you:

- NOT in the Copper! 3D Animation of a Signal Through a VIA | Yuriy Shlepnev: https://youtu.be/yQIBS5xwvVQ

- PCB Layout - Useful Calculations Which You Maybe Didn’t Know About: (with Kenneth Wood) https://youtu.be/fJCRrEf_IH8

- Small Things Damaging Your High Speed Signals (with Bert Simonovich): https://youtu.be/ERvQeln9l-g

gyuunyuu1989 , 04-21-2023, 11:39 AM

I have seen some videos on topic of high speed PCB. They all emphaise strongly on the fact that fields carry the energy and we field needs to be closely coupled to return path of current to prevent the field from spreading. I have seen a few hours of these presentations on Altium and they all continue to talk about this. They also say that via should be avoided if possible. This has made me quite confused for the simple reason that, any real world PCB can't be made without using vias. If I am going to connect a large FPGA to many high speed peripherals (DDR3, transceiver e.t.c), then I shall have to use vias at some point. The issue is simply that the affect of via and how to minimize the problems that via can introduce, I can't find anywhere that this topic is covered. No single resource covers this topic in a comprehensive way. Vias have several attributes, pad size, hole size, what to do with no functional via pads in a multi layer board, where the place the GND vias near signal vias e.t.c.

I appreciate your point about 5GHz frequency although I am not sure how this specific figure has been arrived at. However, digital signals that have short rise time can have frequency components that are in the GHz range. These energies may spread in the PCB and cause problems elsewhere and lead to signal integrity issues.

I appreciate your point about 5GHz frequency although I am not sure how this specific figure has been arrived at. However, digital signals that have short rise time can have frequency components that are in the GHz range. These energies may spread in the PCB and cause problems elsewhere and lead to signal integrity issues.

robertferanec , 04-24-2023, 05:06 AM

What kind of board are you designing? FPGA + DDR3? Maybe it's not necessary overcomplicate nor overthink - these are standard boards. VIAs are not going to damage the signals that much that it would stop working. Of course, use minimum number of VIAs you can and use stitching VIAs where you can.

If you are not sure, you can always simulate it, but from my experience if you don't do something really wrong, this kind of boards will work ok even if you can't follow the practices recommended for 5GHz and more.

If you are not sure, you can always simulate it, but from my experience if you don't do something really wrong, this kind of boards will work ok even if you can't follow the practices recommended for 5GHz and more.

gyuunyuu1989 , 04-26-2023, 11:01 AM

For the last several days, I have seen a large number of youtube videos on the subject of high speed PCB design and have also done a lot of internet searching. There is one specific area that is not being covered in detail anywhere. This is the topic of "via" in PCB high speed tracks.

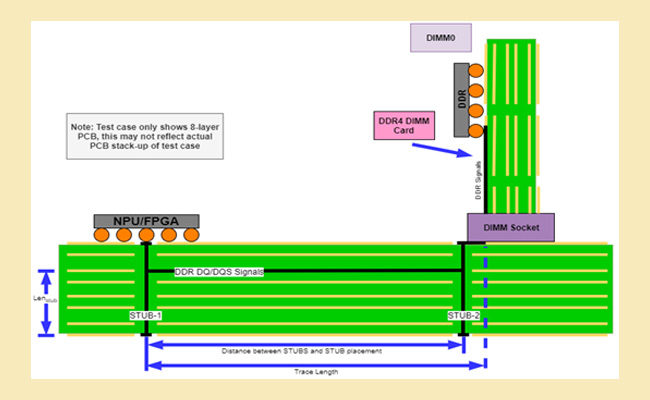

Nowadays we have a lot of components that use BGA which can have a large number of traces. In this case, it might not be possible to route everything on a single layer. We might have a processor or FPGA that uses transceivers and high speed memory interfaces (DDR2/3) that require special care during the PCB layout stage. Here I am only focusing on the signal layout and not the PDN i.e signal integrity.

It is completely clear to me that since the PCB track behaves like a transmission line for high speed signals, we must ensure that the impedance is uniform in the signal travel path to prevent reflections that can corrupt the signal. Also, the signal tracks must not be too close to each other and must have a uniform reference plane that does not have a break in it. Series or parallel termination can be used to improve the signal integrity if the on-chip termination is not present. The characteristic impedance of the track depends on the track width, the copper height, and distance from the GND plane. Everyone talks about this in detail.

Now let's come to via. What I can understand is that the via is like a 90 deg bend in the signal path. By default it has no reference plane unless we put stitching ground vias very close to the signal via. All this means that a via will most likely create an impedance discontinuity that shall cause reflections and signal integrity problems and possibly the EM field carrying the signal to spread and also cause EMC problems. However, no one seems to go into the topic in detail. How do I know what size to use, pad size, hole size? How many GND vias to put and how close? Normal buried via or micro-via? Some resources say that a 3D solver is required to design a via but says no more. Some other resources say don't use via on high speed tracks. Yet, someone even said that via is quite smaller than signal wavelength so it will not cause reflections.

So far it seems that everyone talks about PCB trace impedance subject in immense depth but not go into detail of PCB vias when via is as important as PCB track. So do we avoid via like the plague or just use any random size via and just pray that it works? What is the correct way to use vias in high speed tracks? I will be grateful if you could shed some light on it.

I am looking for correct knowledge on this subject.

Nowadays we have a lot of components that use BGA which can have a large number of traces. In this case, it might not be possible to route everything on a single layer. We might have a processor or FPGA that uses transceivers and high speed memory interfaces (DDR2/3) that require special care during the PCB layout stage. Here I am only focusing on the signal layout and not the PDN i.e signal integrity.

It is completely clear to me that since the PCB track behaves like a transmission line for high speed signals, we must ensure that the impedance is uniform in the signal travel path to prevent reflections that can corrupt the signal. Also, the signal tracks must not be too close to each other and must have a uniform reference plane that does not have a break in it. Series or parallel termination can be used to improve the signal integrity if the on-chip termination is not present. The characteristic impedance of the track depends on the track width, the copper height, and distance from the GND plane. Everyone talks about this in detail.

Now let's come to via. What I can understand is that the via is like a 90 deg bend in the signal path. By default it has no reference plane unless we put stitching ground vias very close to the signal via. All this means that a via will most likely create an impedance discontinuity that shall cause reflections and signal integrity problems and possibly the EM field carrying the signal to spread and also cause EMC problems. However, no one seems to go into the topic in detail. How do I know what size to use, pad size, hole size? How many GND vias to put and how close? Normal buried via or micro-via? Some resources say that a 3D solver is required to design a via but says no more. Some other resources say don't use via on high speed tracks. Yet, someone even said that via is quite smaller than signal wavelength so it will not cause reflections.

So far it seems that everyone talks about PCB trace impedance subject in immense depth but not go into detail of PCB vias when via is as important as PCB track. So do we avoid via like the plague or just use any random size via and just pray that it works? What is the correct way to use vias in high speed tracks? I will be grateful if you could shed some light on it.

I am looking for correct knowledge on this subject.

qdrives , 04-26-2023, 03:33 PM

I do not agree with that. There is plenty on the subject of via's, but.... as @robertferanec already mentioned twice, that become more an isssue on speeds above 5GHz.

Robert made a video with Yuriy Shlepnev - https://www.youtube.com/watch?v=yQIBS5xwvVQ

What is the correct way to use vias in high speed tracks?

In one presentation I seen (sorry I do not know the link anymore) the best size for via's was mentioned as being 0.2mm (tool size)

Then there is back drilling (many video's)

Robert made a video with Yuriy Shlepnev - https://www.youtube.com/watch?v=yQIBS5xwvVQ

What is the correct way to use vias in high speed tracks?

In one presentation I seen (sorry I do not know the link anymore) the best size for via's was mentioned as being 0.2mm (tool size)

Then there is back drilling (many video's)

gyuunyuu1989 , 04-26-2023, 06:34 PM

I shall watch those videos to learn the details. The basic question however, is like this:

Assume the design for DDR3, DDR4 and PCIe gen 4 (I know there is a lot of variation between these)

Do we avoid "via" like the plague or just use any random size via and just pray that it works OR, just use any random via size we like and put GND stitching via somewhere nearby, maybe 1mm or 2mm away.

Assume the design for DDR3, DDR4 and PCIe gen 4 (I know there is a lot of variation between these)

Do we avoid "via" like the plague or just use any random size via and just pray that it works OR, just use any random via size we like and put GND stitching via somewhere nearby, maybe 1mm or 2mm away.

qdrives , 04-27-2023, 01:10 PM

Why a selection in only two extremes?

The size and other specs of the via are not random. They are selected with criteria in mind. But it also depends on how you produce the bare board - like HDI.

If you truly want to know how your design is before going into production, you should simulate it.

And while we are at SIJ:

The size and other specs of the via are not random. They are selected with criteria in mind. But it also depends on how you produce the bare board - like HDI.

If you truly want to know how your design is before going into production, you should simulate it.

And while we are at SIJ:

gyuunyuu1989 , 04-29-2023, 11:05 AM

I am learning PCB design in my free time. I shall look into these links since they contain a lot of knowledge.

As far as simulation is concerned, I have heard that Altium simulation capability is not good. Therefore, one must rely on 3rd party tools like perhaps Hyperlynx, Ansys SI Wave e.t.c. These programs are quite expensive.

As far as simulation is concerned, I have heard that Altium simulation capability is not good. Therefore, one must rely on 3rd party tools like perhaps Hyperlynx, Ansys SI Wave e.t.c. These programs are quite expensive.

Paul van Avesaath , 05-15-2023, 03:40 AM

Do we avoid "via" like the plague or just use any random size via and just pray that it works OR, just use any random via size we like and put GND stitching via somewhere nearby, maybe 1mm or 2mm away.

but your comment on "random size" and "somewhere nearby" is also crap to be honest... it defenitly needs a structure.. keep the distance of sitching via's the same everywhere, also try and play with how your design will look.. install Saturn PCB tool its free and poke around with values.. this way you will get a better understanding of what you are doing.

comments like "lets assume this or that" is not realisitc.. if you want answers you need to be very specific.. otherwise you will get "rule of thumb" remarks like

"in general i always add a minimum of 2 GND via's next to a layerschange of any signal of significant speed.. "

simulation is not a thing within altium as far as SI and High speed is concerned..

hyperlynx and such is expensive yes, but doing several protypes before it works also..

it all depends on what you are designing and if it really needs a simulation.. like <80% of design you do not need a simulation to see if it will work..

Use our interactive Discord forum to reply or ask new questions.